Advanced Encryption Standard Hardware Cryptographic Engine

| Version | Date | Description | Author |

|---|---|---|---|

| 1.0 | 2020/04/17 | NA | PUFsecurity |

For more details, please check out the [ AES repository ]

Features

- symmetric block cipher

- both input and output data are in block of 128 bits in length

- synthesized by Cadence Genus in UMC’s 40nm cell library.

Description

The AES algorithm is an encryption and decryption algorithm that operates on a block-by-block basis, with an input data block of 128 bits in length, and output data block of 128 bits in length. If the input data is over 128 bits in length, it must be broken up into blocks of 128 bits each. AES is a symmetric block cipher algorithm, meaning the same key is used for both encryption and decryption. This design has been synthesized using Cadence Genus with UMC’s 40nm cell library.

Theory of Operations

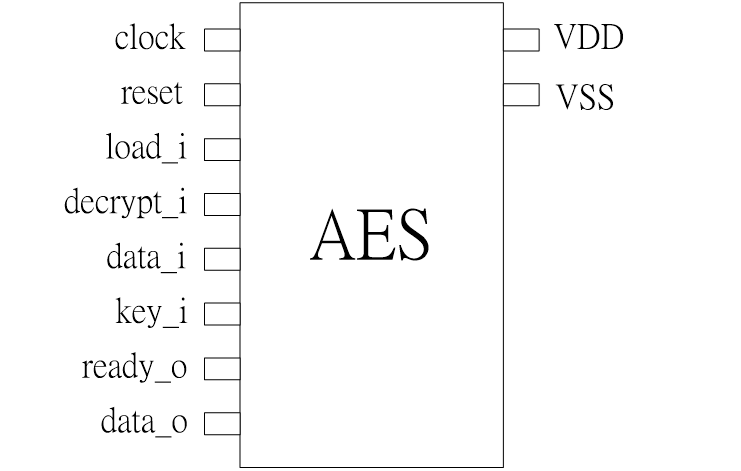

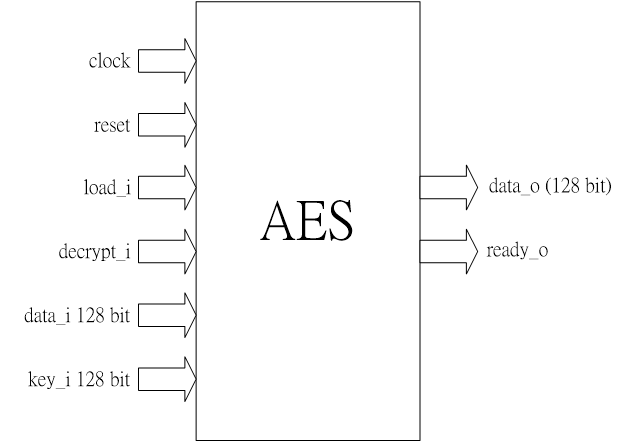

Block Diagram

Hardware Interface

Parameter table

NA

IO table

| Pin Name/Module signal | Direction | Width | Description |

|---|---|---|---|

| Clock/Clock | I | 1bit | System clock |

| reset/reset | I | 1bit | System reset |

| load/load | I | 1bit | Load data |

| decrypt_i/decrypt_i | I | 1bit | Encryption(1)/Decryption(0) |

| data_i/data_i | I | 128bit | Data input |

| key_i/key_i | I | 128bit | key input |

| data_o/data_o | O | 128bit | Data output |

| ready_o/ready_o | O | 1bit | Output ready |

Power Connection Requirement

- Power/Ground bouncing beyond DC specifications is not allowed.

- It is necessary to connect all power sets of VDD/VSS.

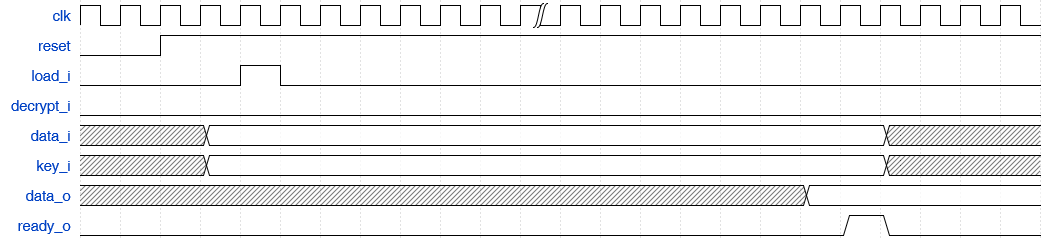

Example Waveform

- Set decrypt_i, data_i and key_i after the reset signal

- After setting the above input signals, an input pulse load_i will start the engine.

- The final result (data_o) is available after the ready_o signal pulses high.

Operation Guideline

Guideline

Note

- The testbench file “final_version_sim.v” uses the NIST test vectors. Please refer to ECBGFSbox128.rsp and ECBKeySbox128.rsp.

- “aes_include.v” contains all necessary module files needed to build the AES engine

Report

| Clock Frequency (MHz) | Throughput (Mb/s) | Gate count (K-gates) | Aera(um*2) | Mode |

|---|---|---|---|---|

| 200 | 198.4 | 11.9 | 6567.9 | Enc/Dec |

Licensing

Unless otherwise noted, everything in this repository is covered by the Apache License, Version 2.0.