Secure Hash Algorithm 2

| Version | Date | Description | Author |

|---|---|---|---|

| 1.0 | 2020/04/17 | NA | PUFsecurity |

For more details, please check out the [ Secure Hash Algorithm 2 repository ]

Features

- NSA designed cryptographic hash

- the engine uses 65 rounds to process each message block(512 bits)

- synthesized by Cadence Genus in UMC’s 40nm cell library.

Description

SHA256 is a cryptographic hash function designed by the United States National Security Agency (NSA) and first published in 2001. Message blocks are 512 bits each and the engine uses 65 rounds to process each message block, returning a digest of 256 bits. This design is synthesized using Cadence Genus with UMC’s 40nm cell library.

Theory of Operations

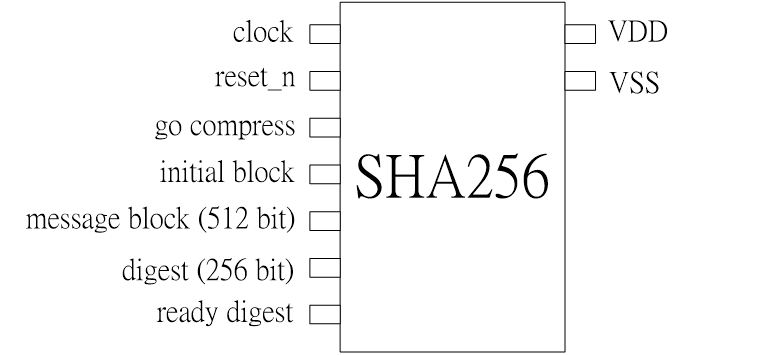

Block Diagram

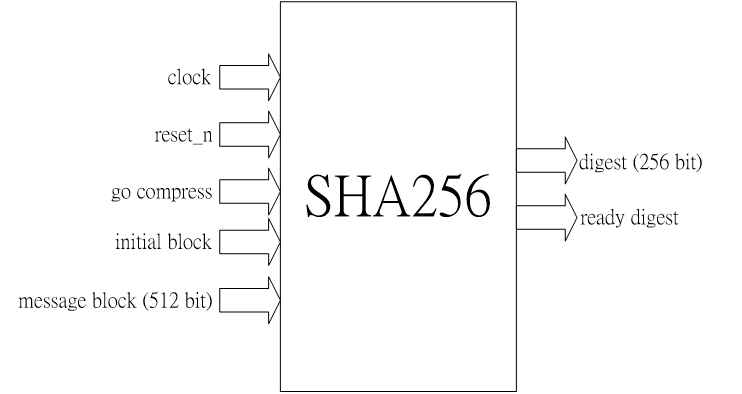

Hardware Interface

Parameter table

NA

IO table

| Pin Name/Module signal | Direction | Width | Description |

|---|---|---|---|

| Clock/clk_osc | I | 1bit | System clock |

| go_compress/go_compress | I | 1bit | Start |

| Initial_block/Initial_block | I | 1bit | First block(1)/not first block(0) |

| message_block /message_block | I | 512bit | Data input |

| reset_n /reset_n | I | 1bit | System reset |

| digest /digest | O | 256bit | Data output |

| ready_digest /ready_digest | O | 1bit | Output ready |

Power Connection Requirement

- Power/Ground bouncing beyond DC specifications is not allowed.

- It is necessary to connect all power sets of VDD/VSS.

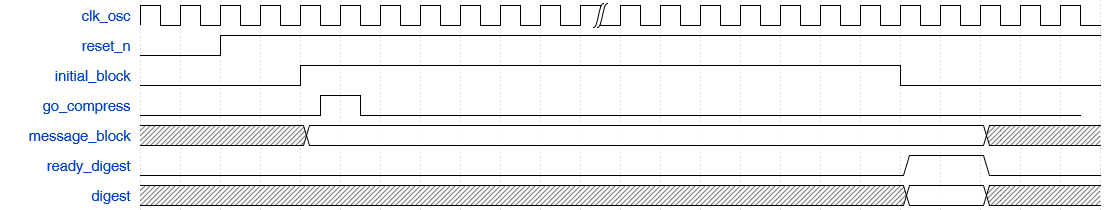

Example Waveform

- Start an operation by bringing initial_block high and using message block to enter the first block of data, after the reset_n signal goes high.

- One half clock after initial block goes high, pulse go compress for one clock period.

- The final result (digest) is available after the ready_digest signal goes high.

Operation Guideline

Guideline

Note

- Input data is 512 bit in length and need to be padded before input to engine.

- The testbench file “sim_top.v” uses NIST test vectors. Please refer to SHA256LongMsg.rsp and SHA256ShortMsg.rsp.

- “sha2_include.v” contains all necessary module files needed to build the SHA2 engine

Report

| Clock Frequency (MHz) | Throughput (Mb/s) | Gate count (K-gates) | Aera(um*2) | Mode |

|---|---|---|---|---|

| 200 | 787.7 | 16.7 | 9143.7 | Enc/Dec |

Licensing

Unless otherwise noted, everything in this repository is covered by the Apache License, Version 2.0.